# STANDARDS

## **IEEE Standard for Ethernet**

# Amendment 5: Physical Layers Specifications and Management Parameters for 10 Mb/s Operation and Associated Power Delivery over a Single Balanced Pair of Conductors

**IEEE Computer Society**

Developed by the LAN/MAN Standards Committee

IEEE Std 802.3cg<sup>™</sup>-2019

(Amendment to IEEE Std 802.3<sup>™</sup>-2018 as amended by IEEE Std 802.3cb<sup>™</sup>-2018, IEEE Std 802.3cd<sup>™</sup>-2018, and IEEE Std 802.3cn<sup>™</sup>-2019)

### IEEE Std 802.3cg™-2019

(Amendment to IEEE Std 802.3™-2018 as amended by IEEE Std 802.3cb™-2018, IEEE Std 802.3cd™-2018, IEEE Std 802.3cd™-2018, and IEEE Std 802.3cn™-2019)

## **IEEE Standard for Ethernet**

# Amendment 5: Physical Layer Specifications and Management Parameters for 10 Mb/s Operation and Associated Power Delivery over a Single Balanced Pair of Conductors

Developed by the

LAN/MAN Standards Committee of the IEEE Computer Society

Approved 7 November 2019

**IEEE SA Standards Board**

**Abstract:** This amendment to IEEE Std 802.3-2018 specifies additions and appropriate modifications to add 10 Mb/s Physical Layer (PHY) specifications and management parameters for operation, and associated optional provision of power, over a single balanced pair of conductors.

**Keywords:** 10BASE-T1L, 10BASE-T1S, amendment, copper, Ethernet, IEEE 802.3™, IEEE 802.3cg™, MASTER-SLAVE, medium dependent interface, physical coding sublayer, Physical Layer Collision Avoidance, PLCA, physical medium attachment

The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA

Copyright © 2020 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 5 February 2020. Printed in the United States of America.

IEEE and 802 are registered trademarks in the U.S. Patent & Trademark Office, owned by The Institute of Electrical and Electronics Engineers, Incorporated.

PDF: ISBN 978-1-5044-6420-8 STD24038 Print: ISBN 978-1-5044-6421-5 STDPD24038

IEEE prohibits discrimination, harassment and bullying.

For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

# Important Notices and Disclaimers Concerning IEEE Standards Documents

IEEE documents are made available for use subject to important notices and legal disclaimers. These notices and disclaimers, or a reference to this page, appear in all standards and may be found under the heading "Important Notices and Disclaimers Concerning IEEE Standards Documents." They can also be obtained on request from IEEE or viewed at http://standards.ieee.org/ipr/disclaimers.html.

## Notice and Disclaimer of Liability Concerning the Use of IEEE Standards Documents

IEEE Standards documents (standards, recommended practices, and guides), both full-use and trial-use, are developed within IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association ("IEEE SA") Standards Board. IEEE ("the Institute") develops its standards through a consensus development process, approved by the American National Standards Institute ("ANSI"), which brings together volunteers representing varied viewpoints and interests to achieve the final product. IEEE Standards are documents developed through scientific, academic, and industry-based technical working groups. Volunteers in IEEE working groups are not necessarily members of the Institute and participate without compensation from IEEE. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

IEEE Standards do not guarantee or ensure safety, security, health, or environmental protection, or ensure against interference with or from other devices or networks. Implementers and users of IEEE Standards documents are responsible for determining and complying with all appropriate safety, security, environmental, health, and interference protection practices and all applicable laws and regulations.

IEEE does not warrant or represent the accuracy or content of the material contained in its standards, and expressly disclaims all warranties (express, implied and statutory) not included in this or any other document relating to the standard, including, but not limited to, the warranties of: merchantability; fitness for a particular purpose; non-infringement; and quality, accuracy, effectiveness, currency, or completeness of material. In addition, IEEE disclaims any and all conditions relating to: results; and workmanlike effort. IEEE standards documents are supplied "AS IS" and "WITH ALL FAULTS."

Use of an IEEE standard is wholly voluntary. The existence of an IEEE standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

In publishing and making its standards available, IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity nor is IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing any IEEE Standards document, should rely upon his or her own independent judgment in the exercise of reasonable care in any given circumstances or, as appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE standard.

IN NO EVENT SHALL IEEE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO: PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE PUBLICATION, USE OF, OR RELIANCE UPON ANY STANDARD, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE AND REGARDLESS OF WHETHER SUCH DAMAGE WAS FORESEEABLE.

### **Translations**

The IEEE consensus development process involves the review of documents in English only. In the event that an IEEE standard is translated, only the English version published by IEEE should be considered the approved IEEE standard.

### Official statements

A statement, written or oral, that is not processed in accordance with the IEEE SA Standards Board Operations Manual shall not be considered or inferred to be the official position of IEEE or any of its committees and shall not be considered to be, or be relied upon as, a formal position of IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position of IEEE.

### Comments on standards

Comments for revision of IEEE Standards documents are welcome from any interested party, regardless of membership affiliation with IEEE. However, IEEE does not provide consulting information or advice pertaining to IEEE Standards documents. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Since IEEE standards represent a consensus of concerned interests, it is important that any responses to comments and questions also receive the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to comments or questions except in those cases where the matter has previously been addressed. For the same reason, IEEE does not respond to interpretation requests. Any person who would like to participate in revisions to an IEEE standard is welcome to join the relevant IEEE working group.

Comments on standards should be submitted to the following address:

Secretary, IEEE SA Standards Board 445 Hoes Lane Piscataway, NJ 08854 USA

### Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the provisions of any IEEE Standards document does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

### Copyrights

IEEE draft and approved standards are copyrighted by IEEE under US and international copyright laws. They are made available by IEEE and are adopted for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making these documents available for use and adoption by public authorities and private users, IEEE does not waive any rights in copyright to the documents.

### **Photocopies**

Subject to payment of the appropriate fee, IEEE will grant users a limited, non-exclusive license to photocopy portions of any individual standard for company or organizational internal use or individual, non-commercial use only. To arrange for payment of licensing fees, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

### **Updating of IEEE Standards documents**

Users of IEEE Standards documents should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect.

Every IEEE standard is subjected to review at least every 10 years. When a document is more than 10 years old and has not undergone a revision process, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE standard.

In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit IEEE Xplore at <a href="https://ieeexplore.ieee.org">https://ieeexplore.ieee.org</a> or contact IEEE at the address listed previously. For more information about the IEEE SA or IEEE's standards development process, visit the IEEE SA Website at <a href="https://standards.ieee.org">https://standards.ieee.org</a>.

### **Errata**

Errata, if any, for IEEE standards can be accessed via <a href="https://standards.ieee.org/standard/index.html">https://standards.ieee.org/standard/index.html</a>. Search for standard number and year of approval to access the web page of the published standard. Errata links are located under the Additional Resources Details section. Errata are also available in IEEE Xplore: <a href="https://ieeexplore.ieee.org/browse/standards/collection/ieee/">https://ieeexplore.ieee.org/browse/standards/collection/ieee/</a>. Users are encouraged to periodically check for errata.

### **Patents**

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE SA Website at <a href="https://standards.ieee.org/about/sasb/patcom/patents.html">https://standards.ieee.org/about/sasb/patcom/patents.html</a>. Letters of Assurance may indicate whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

### **Participants**

Piers Dawe

Fred Dawson

The following individuals were officers and members of the IEEE 802.3 Working Group at the beginning of the IEEE P802.3cg Working Group ballot.

David J. Law, IEEE 802.3 Working Group Chair Adam Healey, IEEE 802.3 Working Group Vice-Chair Pete Anslow, IEEE 802.3 Working Group Secretary Steven B. Carlson, IEEE 802.3 Working Group Executive Secretary Valerie Maguire, IEEE 802.3 Working Group Treasurer

George Zimmerman, IEEE P802.3cg 10 Mb/s Single-Pair Ethernet Task Force Chair Valerie Maguire, IEEE P802.3cg 10 Mb/s Single-Pair Ethernet Task Force Editor-in-Chief

Gerrit den Besten John Abbott Gergely Huszak David Abramson Claudio DeSanti Yasuhiro Hyakutake Andrea Agnes Eric DiBiaso Jonathan Ingham Dale Amason Chris Diminico Alessandro Ingrassia Richard Baca Hormoz Djahanshahi Kazuhiko Ishibe **Amrik Bains** Curtis Donahue Hideki Isono Thananya Baldwin Liang Du Tom Issenhuth Denis Beaudoin Mike Dudek Kenneth Jackson Francois Beauregard Frank Effenberger Andrew Jimenez Piergiorgio Beruto David Estes John Johnson Vipul Bhatt John Ewen Chad Jones Gao Bo Ramin Farjad Peter Jones Brad Booth Borhan Fathi Moghadam Lokesh Kabra Shahar Feldman Martin Bouda Manabu Kagami David Brandt Vincent Ferretti Upen Kareti Ralf-Peter Braun Alan Flatman Yasuaki Kawatsu Theodore Brillhart Brian Franchuk Yong Kim Paul Brooks Matthias Fritsche Mark Kimber Alan Brown Richard Frosch Andrew Klaus Matthew Brown Mike Gardner Michael Klempa Phillip Brownlee Claude Gauthier Curtis Knittle Michal Brychta Ali Ghiasi

Elizabeth Kochuparambil Chris Bullock Joel Goergen Paul Kolesar Gary Burrell **Zhigang Gong** Taiji Kondo Jairo Bustos Heredia Steven Gorshe Glen Kramer Adrian Butter Jens Gottron Olaf Krieger John Calvin Steffen Graber Hans Lackner Clark Carty Olaf Grau Jeffrey Lapak Craig Chabot Robert Grow Mark Laubach Mandeep Chadha Yong Guo Greg Le Cheminant David Chalupsky Mark Gustlin Han Hvub Lee Frank Chang Marek Hajduczenia June Hee Lee Xin Chang Akinori Hayakawa David Lewis Chan Chen Hayden Haynes Jon Lewis Weiying Cheng Howard Heck David Li Golam Choudhury Rajmohan Hegde Mike-Peng Li Keng Hua Chuang David Hess Jane Lim Keith Conroy Yasuo Hidaka Alex Lin John D'Ambrosia Brian Holden Robert Lingle Yair Darshan Rita Horner Dekun Liu

Bernd Horrmeyer

Xi Huang

Hai-Feng Liu

Karen Liu

Zhenyu Liu Miklos Lukacs Kent Lusted Zahy Madgar Jefferv Maki David Malicoat Arthur Marris Takeo Masuda Kirsten Matheus Erdem Matoglu Marco Mazzini Mick McCarthy Brett McClellan Larry McMillan Greg McSorley Marcel Medina Richard Mellitz Phil Miguelez Martin Miller Toshiyuki Moritake Harald Mueller Thomas Mueller **Edward Nakamoto** Paul Neveux Gary Nicholl John Nolan Kevin Noll Ronald Nordin Mark Nowell David Ofelt Josef Ohni Tom Palkert Sujan Pandey Earl Parsons Arkadiy Peker Gerald Pepper Phong Pham

Dino Pozzebon Rick Rabinovich Adee Ran Alon Regev Duane Remein Victor Renteria Michael Ressl Salvatore Rotolo Alexander Rysin Toshiaki Sakai Sam Sambasivan **Edward Sayre** James Schuessler Steve Sekel Masood Shariff Ramin Shirani Mizuki Shirao Kapil Shrikhande Jeff Slavick Daniel Smith Scott Sommers Bryan Sparrowhawk Edward Sprague Peter Stassar Heath Stewart David Stover Junqing Sun Liyang Sun Steve Swanson Andre Szczepanek **Bharat Tailor** Tomoo Takahara Kohichi Tamura Mehmet Tazebay Ronald Tellas Geoffrey Thompson Pirooz Tooyserkani

Stephen Trowbridge Ta Chin Tseng Ed Ulrichs Daisuke Umeda Alexander Umnov Sterling A. Vaden Paul Vanderlaan Ricky Vernickel Marco Vitali Robert Voss Dylan Walker Edward Walter Haifei Wang Roy Wang Tongtong Wang Xinyuan Wang Christoph Wechsler Brian Welch Matthias Wendt Natalie Wienckowski Ludwig Winkel James Withey Peter Wu Markus Wucher Dayin Xu Yu Xu Shuto Yamamoto

Adrian Young

James Young

Lennart Yseboodt

Andrew Zambell

Conrad Zerna

Richard (Yujia) Zhou

Yan Zhuang

Martin Zielinski

Pavel Zivny

Harald Zweck

The following members of the individual balloting committee voted on this amendment. Individuals may have not voted, voted for approval, disapproval or abstained on this standard.

Nathan Tracy

Matthew Traverso

David Tremblay

Robert Aiello Thomas Alexander Richard Alfvin Dale Amason Hongming An Pete Anslow **Butch Anton** Tim Baggett Michael Bahr **Amrik Bains** Gordon Bechtel Piergiorgio Beruto Burrell Best Rich Boyer David Brandt Ralf-Peter Braun Nancy Bravin

David Piehler

Rick Pimpinella

William Powell

Theodore Brillhart Michal Brychta Demetrio Bucaneg Jairo Bustos Heredia William Byrd Steven B. Carlson Clark Carty John Deandrea Chris Diminico Brian Franchuk Avraham Freedman Matthias Fritsche Claude Gauthier Devon Gayle Joel Goergen **Zhigang Gong** Steffen Graber

Scott Griffiths

Randall Groves

Robert Grow

Marek Hajduczenia

Adam Healey

Marco Hernandez

Werner Hoelzl

David Hoglund

Gergely Huszak

Yasuhiro Hyakutake

Atsushi Ito

Raj Jain

Sang Kwon Jeong

Raj Jain Sang Kwon Jeong Chad Jones Peter Jones Lokesh Kabra Manabu Kagami

Piotr Karocki Stuart Kerry Yongbum Kim Wojciech Koczwara Taiji Kondo Robert Landman Mark Laubach David J. Law Hyeong Ho Lee David Lewis Jon Lewis Michael Lynch Valerie Maguire Jeffery Maki Nicolai Malykh Arthur Marris Michael Maytum Mick McCarthy Brett McClellan Larry McMillan Richard Mellitz Martin Miller Jose Morales Henry Muyshondt Paul Neveux

Nick S. A. Nikjoo Paul Nikolich Mark Nowell Satoshi Obara Tom Palkert Carlos Pardo Bansi Patel David Piehler Rick Pimpinella Christopher Pohl William Quackenbush R. K. Rannow Alon Regev Thomas Rettig Maximilian Riegel Gary Robinson Robert Robinson Toshiaki Sakai

Michael Thompson

Nathan Tracy

David Tremblay

Mark-Rene Uchida

Dmitri Varsanofiev

George Vlantis

Robert Voss

Lisa Ward

Keith Waters

Karl Weber

Matthias Wendt

Scott Willy

Ludwig Winkel

James Withey

Peter Wu

Dayin Xu

Lennart Yseboodt

Oren Yuen

Junqing Sun

Geoffrey Thompson

Toshiaki Sakai Dayin Xu

Nicola Scantamburlo Lennart Yseboodt

Dieter Schicketanz Oren Yuen

Michael Seaman Zhen Zhou

Thomas Starai Dirk Ziegelmeier

Heath Stewart Martin Zielinski

Walter Struppler George Zimmerman

Mitsutoshi Sugawara Pavel Zivny

When the IEEE SA Standards Board approved this amendment on 7 November 2019, it had the following membership:

Gary Hoffman, Chair Ted Burse, Vice Chair Jean-Philippe Faure, Past Chair Konstantinos Karachalios, Secretary

Masayuki Ariyoshi Stephen D. Dukes J. Travis Griffith Guido Hiertz Christel Hunter Joseph L. Koepfinger\* Thomas Koshy John D. Kulick David J. Law Joseph Levy Howard Li Xiaohui Liu Kevin Lu Daleep Mohla Andrew Myles Annette Reilly

Dorothy Stanley

Sha Wei

Phil Wennblom

Philip Winston

Howard Wolfman

Feng Wu

Jingyi Zhou

<sup>\*</sup>Member Emeritus

### Introduction

This introduction is not part of IEEE Std 802.3cg-2019, IEEE Standard for Ethernet—Amendment 5: Physical Layer Specifications and Management Parameters for 10 Mb/s Operation and Associated Power Delivery over a Single Balanced Pair of Conductors.

IEEE Std 802.3<sup>TM</sup> was first published in 1985. Since the initial publication, many projects have added functionality or provided maintenance updates to the specifications and text included in the standard. Each IEEE 802.3 project/amendment is identified with a suffix (e.g., IEEE Std 802.3ba<sup>TM</sup>-2010).

The half duplex Media Access Control (MAC) protocol specified in IEEE Std 802.3-1985 is Carrier Sense Multiple Access with Collision Detection (CSMA/CD). This MAC protocol was key to the experimental Ethernet developed at Xerox Palo Alto Research Center, which had a 2.94 Mb/s data rate. Ethernet at 10 Mb/s was jointly released as a public specification by Digital Equipment Corporation (DEC), Intel and Xerox in 1980. Ethernet at 10 Mb/s was approved as an IEEE standard by the IEEE Standards Board in 1983 and subsequently published in 1985 as IEEE Std 802.3-1985. Since 1985, new media options, new speeds of operation, and new capabilities have been added to IEEE Std 802.3. A full duplex MAC protocol was added in 1997.

Some of the major additions to IEEE Std 802.3 are identified in the marketplace with their project number. This is most common for projects adding higher speeds of operation or new protocols. For example, IEEE Std 802.3u<sup>TM</sup> added 100 Mb/s operation (also called Fast Ethernet), IEEE Std 802.3z added 1000 Mb/s operation (also called Gigabit Ethernet), IEEE Std 802.3ae added 10 Gb/s operation (also called 10 Gigabit Ethernet), IEEE Std 802.3ah<sup>TM</sup> specified access network Ethernet (also called Ethernet in the First Mile) and IEEE Std 802.3ba added 40 Gb/s operation (also called 40 Gigabit Ethernet) and 100 Gb/s operation (also called 100 Gigabit Ethernet). These major additions are all now included in and are superseded by IEEE Std 802.3-2018 and are not maintained as separate documents.

At the date of publication for IEEE Std 802.3cg-2019, IEEE Std 802.3 was composed of the following documents:

### IEEE Std 802.3-2018

Section One—Includes Clause 1 through Clause 20 and Annex A through Annex H and Annex 4A. Section One includes the specifications for 10 Mb/s operation and the MAC, frame formats and service interfaces used for all speeds of operation.

Section Two—Includes Clause 21 through Clause 33 and Annex 22A through Annex 33E. Section Two includes management attributes for multiple protocols and speed of operation as well as specifications for providing power over twisted pair cabling for multiple operational speeds. It also includes general information on 100 Mb/s operation as well as most of the 100 Mb/s Physical Layer specifications.

Section Three—Includes Clause 34 through Clause 43 and Annex 36A through Annex 43C. Section Three includes general information on 1000 Mb/s operation as well as most of the 1000 Mb/s Physical Layer specifications.

Section Four—Includes Clause 44 through Clause 55 and Annex 44A through Annex 55B. Section Four includes general information on 10 Gb/s operation as well as most of the 10 Gb/s Physical Layer specifications.

Section Five—Includes Clause 56 through Clause 77 and Annex 57A through Annex 76A. Clause 56 through Clause 67 and Clause 75 through Clause 77, as well as associated annexes, specify subscriber

access and other Physical Layers and sublayers for operation from 512 kb/s to 10 Gb/s, and defines services and protocol elements that enable the exchange of IEEE Std 802.3 format frames between stations in a subscriber access network. Clause 68 specifies a 10 Gb/s Physical Layer specification. Clause 69 through Clause 74 and associated annexes specify Ethernet operation over electrical backplanes at speeds of 1000 Mb/s and 10 Gb/s.

Section Six—Includes Clause 78 through Clause 95 and Annex 83A through Annex 93C. Clause 78 specifies Energy-Efficient Ethernet. Clause 79 specifies IEEE 802.3 Organizationally Specific Link Layer Discovery Protocol (LLDP) type, length, and value (TLV) information elements. Clause 80 through Clause 95 and associated annexes include general information on 40 Gb/s and 100 Gb/s operation as well the 40 Gb/s and 100 Gb/s Physical Layer specifications. Clause 90 specifies Ethernet support for time synchronization protocols.

Section Seven—Includes Clause 96 through Clause 115 and Annex 97A through Annex 115A. Clause 96 through Clause 98, Clause 104, and associated annexes, specify Physical Layers and optional features for 100 Mb/s and 1000 Mb/s operation over a single twisted pair. Clause 100 through Clause 103, as well as associated annexes, specify Physical Layers for the operation of the EPON protocol over coaxial distribution networks. Clause 105 through Clause 114 and associated annexes include general information on 25 Gb/s operation as well as 25 Gb/s Physical Layer specifications. Clause 99 specifies a MAC merge sublayer for the interspersing of express traffic. Clause 115 and its associated annex specify a Physical Layer for 1000 Mb/s operation over plastic optical fiber.

Section Eight—Includes Clause 116 through Clause 126 and Annex 119A through Annex 120E. Clause 116 through Clause 124 and associated annexes include general information on 200 Gb/s and 400 Gb/s operation as well the 200 Gb/s and 400 Gb/s Physical Layer specifications. Clause 125 and Clause 126 include general information on 2.5 Gb/s and 5 Gb/s operation as well as 2.5 Gb/s and 5 Gb/s Physical Layer specifications.

### IEEE Std 802.3cbTM-2018

Amendment 1—This amendment includes changes to IEEE Std 802.3-2018 and its amendments and adds Clause 127 through Clause 130, Annex 127A, Annex 128A, Annex 128B, and Annex 130A. This amendment adds new Physical Layers for operation at 2.5 Gb/s and 5 Gb/s over electrical backplanes.

### IEEE Std 802.3btTM-2018

Amendment 2—This amendment includes changes to IEEE Std 802.3-2018 and its amendments and adds Clause 145, Annex 145A, Annex 145B, and Annex 145C. This amendment adds power delivery using all four pairs in the structured wiring plant, resulting in greater power being available to end devices. This amendment also allows for lower standby power consumption in end devices and adds a mechanism to better manage the available power budget.

### IEEE Std 802.3cdTM-2018

Amendment 3—This amendment includes changes to IEEE Std 802.3-2018 and its amendments and adds Clause 131 through Clause 140 and Annex 135A through Annex 136D. This amendment adds MAC parameters, Physical Layers, and management parameters for the transfer of IEEE 802.3 format frames at 50 Gb/s, 100 Gb/s, and 200 Gb/s.

### IEEE Std 802.3cn<sup>TM</sup>-2019

Amendment 4—This amendment includes changes to IEEE Std 802.3-2018 and its amendments and adds 50 Gb/s, 200 Gb/s, and 400 Gb/s Physical Layer specifications and management parameters for operation over single-mode fiber with reaches of at least 40 km.

### IEEE Std 802.3cg<sup>TM</sup>-2019

Amendment 5—This amendment includes changes to IEEE Std 802.3-2018 and its amendments and adds Clause 146 through Clause 148 and Annex 146A and Annex 146B. This amendment adds 10 Mb/s Physical Layer specifications and management parameters for operation on a single balanced pair of conductors.

Two companion documents exist, IEEE Std 802.3.1 and IEEE Std 802.3.2. IEEE Std 802.3.1 describes Ethernet management information base (MIB) modules for use with the Simple Network Management Protocol (SNMP). IEEE Std 802.3.2 describes YANG data models for Ethernet. IEEE Std 802.3.1 and IEEE Std 802.3.2 are updated to add management capability for enhancements to IEEE Std 802.3 after approval of those enhancements.

IEEE Std 802.3 will continue to evolve. New Ethernet capabilities are anticipated to be added within the next few years as amendments to this standard.

### **Contents**

| 1.  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 1.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26 |

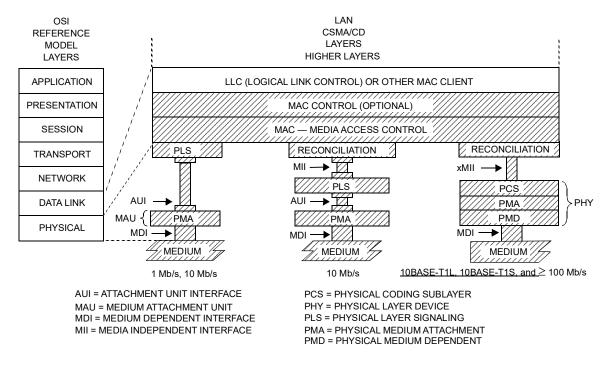

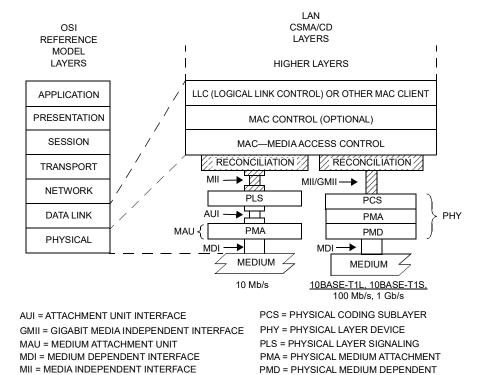

|     | 1.1.3 Architectural perspectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|     | 1.3 Normative references                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|     | 1.4 Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|     | 1.5 Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 9.  | Repeater unit for 10 Mb/s baseband networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30 |

| 9.  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|     | 9.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30 |

| 22. | Reconciliation Sublayer (RS) and Media Independent Interface (MII)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31 |

|     | 22.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31 |

|     | 22.2 Functional specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31 |

|     | 22.2.2 MII signal functional specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31 |

|     | 22.2.2.4 TXD (transmit data)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31 |

|     | 22.2.2.5 TX ER (transmit coding error)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32 |

|     | 22.2.2.8 RXD (receive data)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|     | 22.8 Protocol implementation conformance statement (PICS) proforma for Clause 22,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|     | Reconciliation Sublayer (RS) and Media Independent Interface (MII)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

|     | 22.8.2 Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|     | 22.8.2.3 Major capabilities/options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | 22.8.3 PICS proforma tables for reconciliation sublayer and media independent interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|     | 22.8.3.2 MII signal functional specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|     | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |